## ME ELX SEM-II (CBEGS) SWD-DDRA DT:17-52017

QP Code: 13829

(3 Hours)

[ Total Marks: 80

| N.B.: (1) Question No. 1 is comp | pulsor | V |

|----------------------------------|--------|---|

|----------------------------------|--------|---|

- Attempt any three questions out of remaining five. (2)

- Each question carries 20 marks and sub-questions carry equal marks. (3)

- Assume suitable data if required. (4)

- (a) Draw the state diagram for non-overlapping sequence "1100".

- (b) What is the difference between signal and variable.

- (c) Explain various elements used in ASM charts.

- (d) Explain the clock management used in FPGA.

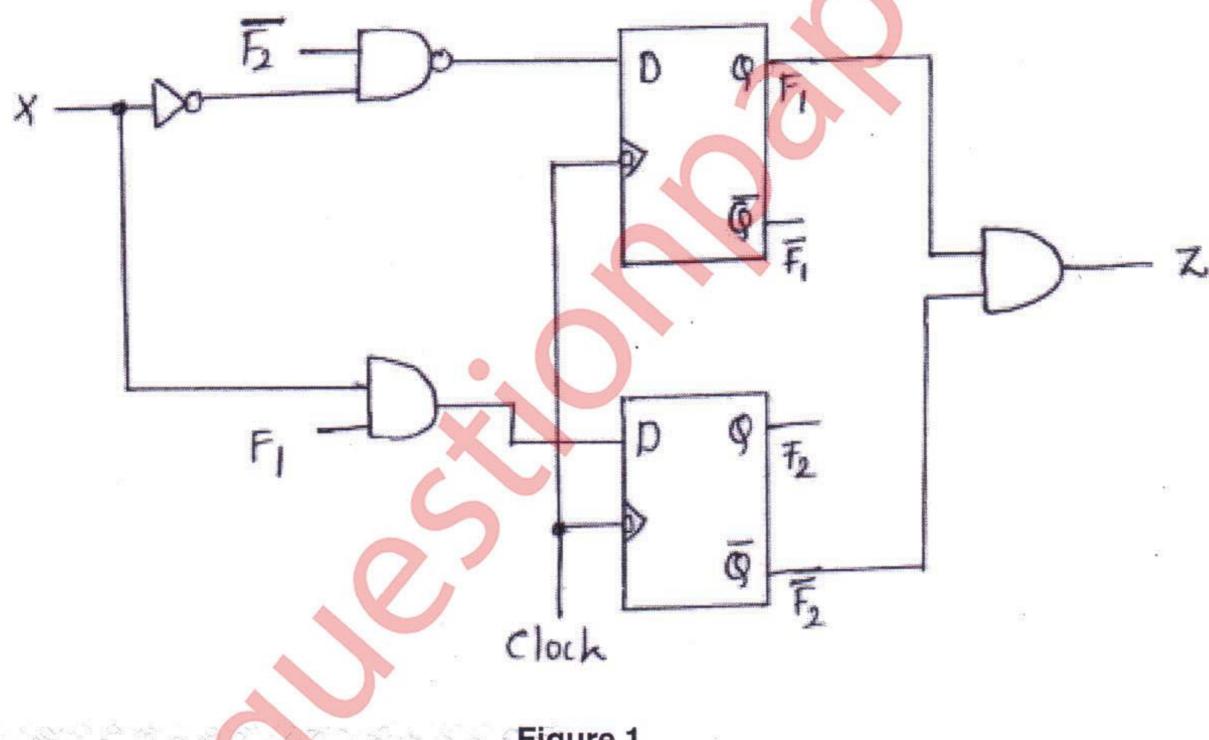

- (a) For the given logic diagram in Figure 1 below, draw the state diagram

- 5

- 5

- 10

Figure 1

[ TURN OVER

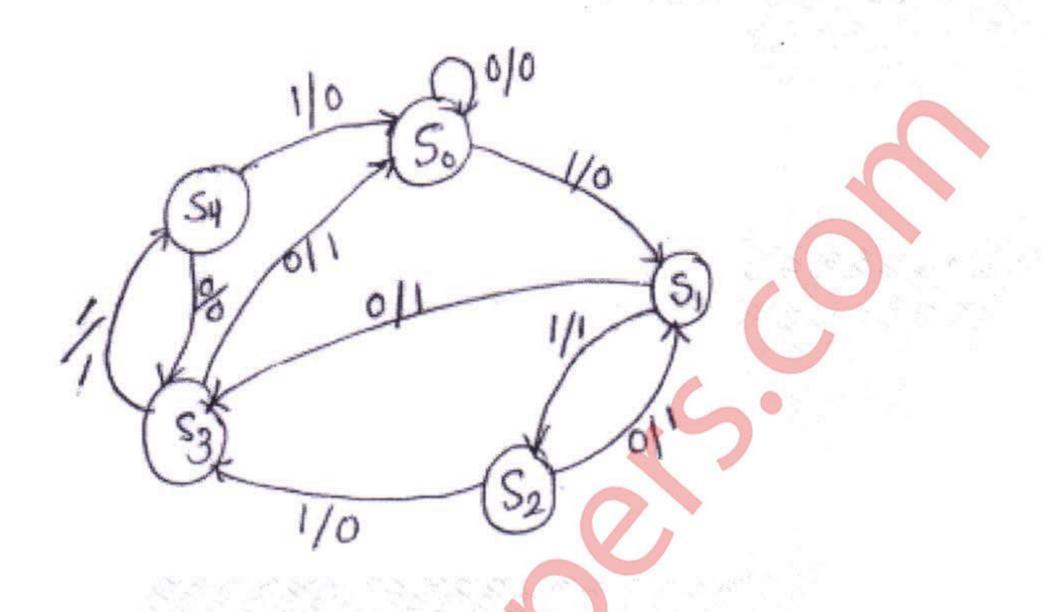

(b) A state diagram of a sequential machine is shown in Figure 2 below. Recognize the type of machine. Identify the redundent state. Obtain the simplified state diagram. Also design the machine.

Figure 2

| 3. | <ul><li>(a) Draw state diagram for BCD counter. Write a VHDL code for this state machine.</li><li>(b) Write a VHDL code for shift register. Use "Generic" and attributes in the code. List all the attributes used.</li></ul> | 10<br>10 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4. | (a) Using Data / controller partioning method. Draw ASM charts for bit counting circuit and explain it.                                                                                                                       | 10       |

|    | (b) Using WITH / SELECT / WHEN write a VHDL code for 8 : 1 multiplexer.                                                                                                                                                       | 10       |

| 5. | (a) Explain in detail the structure of SRAM based FPGA.                                                                                                                                                                       | 10       |

|    | (b) Write VHDL code for 4 bit carry look ahead adder.                                                                                                                                                                         | 10       |

| 6. | Write short notes on any three of the following :—  (a) RTL Simulation                                                                                                                                                        | 20       |

|    | (b) Data Types in VHDL                                                                                                                                                                                                        |          |

|    | (c) State Reduction Techniques                                                                                                                                                                                                |          |

(d) ARRAYS in VHDL.