## Paper / Subject Code: 51203 / Digital System Design

**Time: 3 Hours**

20-Nov-2019 1T01023 - S.E.(Electronic & Telecommunication Engineering)(SEM-III)(Choice Base) / 51203 - Digital System Design 77729

Max Marks: 80

|     | N:B        | <ol> <li>Question No. 1 is compulsory.</li> <li>Out of remaining questions, attempt any three questions.</li> <li>Assume suitable additional data if required.</li> <li>Figures in brackets on the right hand side indicate full marks.</li> </ol>                                                                                                                       |              |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Q.1 | (A)        | The Gray code for decimal number 6 is equivalent to i) 0100                                                                                                                                                                                                                                                                                                              | (01)<br>(04) |

|     | (B)        | Which of the following is correct statement:  i) PLA contains a fixed AND array and a programmable OR array.  ii) PLA contains a programmable AND array and a programmable OR array.  iii) PAL contains a fixed AND array and a programmable OR array.  iv) PAL contains a programmable AND array and a programmable OR array.  Draw the structure of correct statement. | (01)         |

|     | (C)        | Which of the following expression is equivalent to $Z = A B + C$ where $A$ represents MSB and $C$ represents LSB of the binary numbers?<br>i) $Z = \sum m(0, 2, 6)$ .<br>ii) $Z = \prod M(1, 3, 4, 5, 7)$ .<br>iii) $Z = \prod M(0, 2, 6)$ .<br>Prove it.                                                                                                                | (01)         |

|     | (D)        | A single 4-bit magnitude comparator IC 7485 can compare maximum i) two 4-bit numbers ii) two 5-bit numbers iii) two 8-bit numbers iv) two 10-bit numbers Draw its corresponding diagram                                                                                                                                                                                  | (01)         |

| Q.2 | (A)        | Implement the following Boolean equation using single 4:1 MUX and few logic gates: $F(A, B, C, D) = \sum_{i=1}^{n} m(0, 2, 5, 6, 7, 9, 12, 15)$ .                                                                                                                                                                                                                        | (10)         |

|     | (B)        | Write the VHDL code for Fibonacci Series Generator sequential circuit.                                                                                                                                                                                                                                                                                                   | (10)         |

| Q.3 | (A)        | Design synchronous counter using D type flip flops for getting the following sequence: $0 \rightarrow 2 \rightarrow 4 \rightarrow 6 \rightarrow 0$ .  Take care of lockout condition.                                                                                                                                                                                    | (10)         |

|     | (B)<br>(C) | Compare SRAM with DRAM.                                                                                                                                                                                                                                                                                                                                                  | (05)<br>(05) |

| Q.4 | (A)<br>(B) | Draw a neat circuit of BCD adder using IC 7483 and explain. Using Quine Mc'Clusky method, minimize the following: $F(A,B,C,D) = \sum_{i=1}^{n} m(0,3,5,7,8,11,13,15)$ .                                                                                                                                                                                                  | (10)<br>(10) |

- Q.5 (A) With neat diagram, explain the working of Universal Shift Registers. Give its applications. (10)

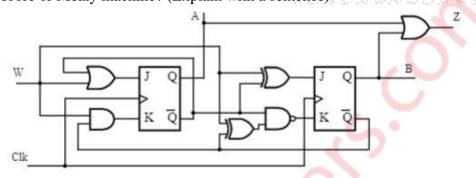

- (B) Analyze the circuit given in Figure 5(B). Assume initial state as A=0, B=0. (10) Complete a state table that shows the behavior of this state machine. Is this a Moore or Mealy machine? (Explain with a sentence)

Fig. 5(B)

- **6.** (A) Convert T type flip flop into D type flip flop.

- (B) Compare Moore with Mealy circuits. (05)

(05)

- (C) Compare PAL with PLA. (05)

- (D) Compare FPGA with CPLD. (05)

\*\*\*\*\*\*\*

77729 Page 2 of 2